#320 Synchronous JK Counter

A synchronous 8-bit counter built with JK Flip-Flops.

Here’s a quick video of the circuit in action:

Notes

A synchronous counter changes its output bits simultaneously, with no ripple. This contrasts with an asynchronous counter that changes its output bits in a ripple, as demonstrated by LEAP#186 AsyncJKCounter.

This project implements a classic synchronous counter design using JK flip-flops and AND gates.

How it Works

As with the asynchronous counter, the mechanism relies on the fact that in a binary sequence, the next highest bit transitions high when the previous lower bit transitions low:

| q2 | q1 | q0 | Note |

|---|---|---|---|

| 0 | 0 | 0 | q0 is directly toggled by the clock |

| 0 | 0 | 1 | q0 is directly toggled by the clock |

| 0 | 1 | 0 | q1 goes high when q0 goes low |

| 0 | 1 | 1 | |

| 1 | 0 | 0 | q2 goes high when q1 goes low |

The circuit comprises chained 74LS73 Dual JK Flip-Flops with Clear and 74LS08 Quad 2-input AND gates.

As all the J-K inputs are ganged together, with clear inputs pinned high, only two states of the truth table apply:

| CLR | CLK | J | K | Q | Q’ | Note |

|---|---|---|---|---|---|---|

| 1 | 1 -> 0 | 0 | 0 | Qo | Qo’ | i.e. unchanged |

| 1 | 1 -> 0 | 1 | 1 | Qo’ | Qo | i.e. toggle |

The cascading of the change is achieved with the AND gate which combines the input and output of the previous JK flip-flop to set the input to the next JK flip-flop.

- this sets the input to the next JK flip-flop high when the previous two “bits” are high

- when the clock ticks, this causes the output of the next JK flip-flop to toggle

Construction

Breadboard build:

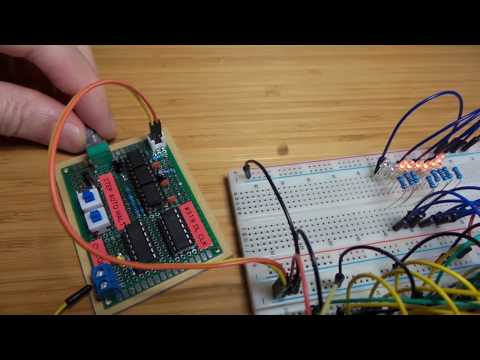

Breadboard test:

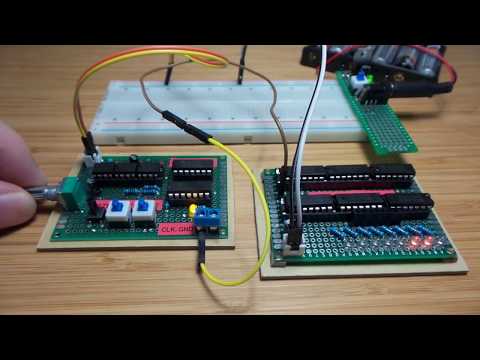

Protoboard build:

Credits and References

- 74LS73 Datasheet

- 74LS08 Datasheet

- LEAP#186 AsyncJKCounter - asynchronous 4-bit counter using JK Flip-Flops

- Synchronous Counter - wikipedia

- Synchronous Counters

- BCD or Decade Counter

- BCD Counter Circuit

- Synchronous Counters - Final Report

- Digital Counters

- ..as mentioned on my blog